# First Time, Every Time – Practical Tips for Phase-Locked Loop Design

Dennis Fischette Email: pll@delroy.com Website: http://www.delroy.com

## Outline

- Introduction

- Basic Feedback Loop Theory

- Jitter and Phase Noise

- Common Circuit Implementations

- Circuit Verification

- Design for Test

### Introduction

Copyright, Dennis Fischette, 2009

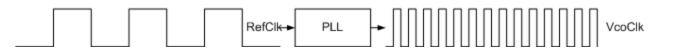

### How Are PLL's Used?

• Frequency Synthesis (e.g. generating a 1 GHz clock from a 100 MHz reference in a CPU)

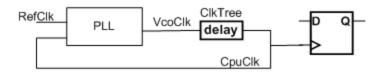

• Skew Cancellation (e.g. phase-aligning an internal clock to the I/O clock) (May use a DLL instead)

### How Are PLL's Used?

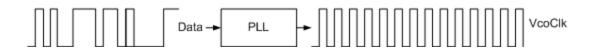

Extracting a clock from a random data stream (e.g. seriallink clock-data recovery)

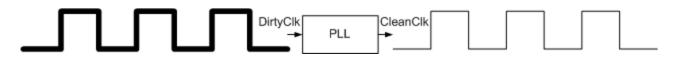

Reference Clean-Up (e.g. low-pass filter source-synchronous clock in high-speed I/O)

- Frequency Synthesis is the focus of this course.

- Design Priority? Frequency and/or phase accuracy?

### What is a PLL?

- Negative feedback control system where  $f_{out}$  tracks  $f_{in}$  and rising edges of input clock align to rising edges of output clock

- Mathematical model of frequency synthesizer

$$V_{in}(t) \propto \sin\left(2\pi f_{in}t\right) \longrightarrow \begin{bmatrix} \mathsf{Phase-}\\ \mathsf{Locked}\\ \mathsf{Loop} \end{bmatrix} \longrightarrow V_{out}(t) \propto \sin\left(2\pi N f_{in}t\right)$$

• Phase = ∫ frequency

$$\phi(t) = 2\pi \int f(t) dt \iff f(t) = \frac{1}{2\pi} \frac{d\phi(t)}{dt}$$

When phase-locked,

$$\phi_{out} = N\phi_{in} \rightarrow f_{out} = Nf_{in}$$

Copyright, Dennis Fischette, 2009

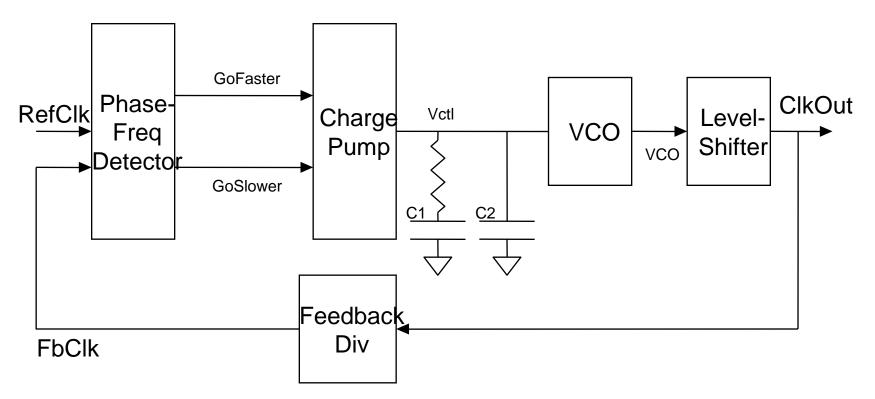

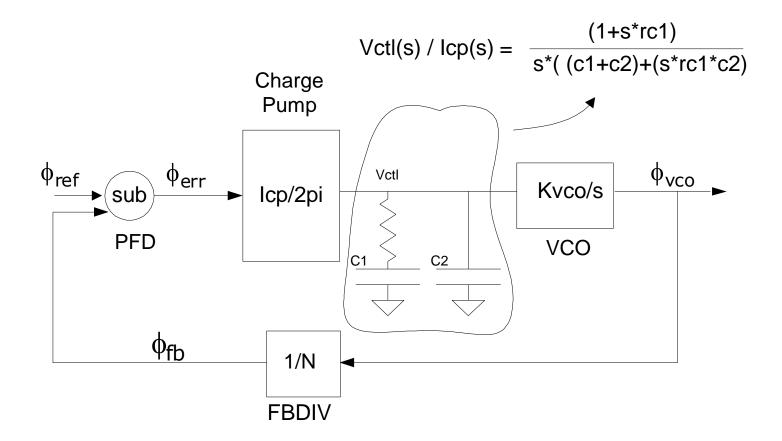

### Charge-Pump PLL Block Diagram

- Sampled-system (phase-error is input variable)

- Phase error is corrected by changing frequency ( $\phi(t) = \int f(t) dt$ )

- Resistor provides means to separate correction of frequency error from correction of phase error

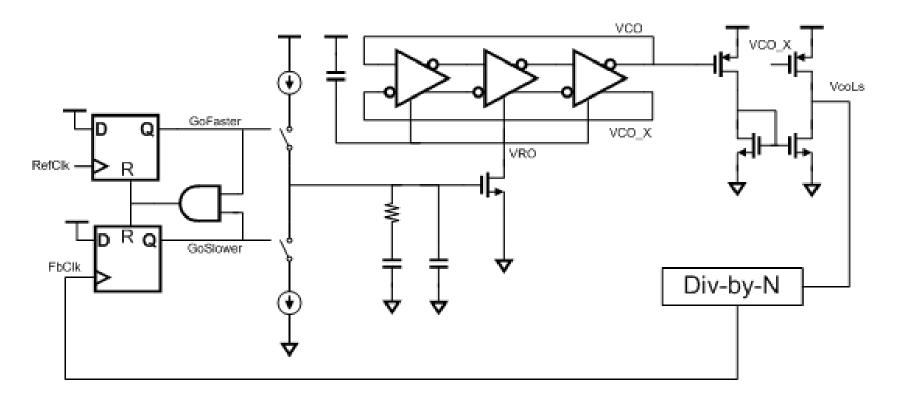

#### PLL Circuit Diagram

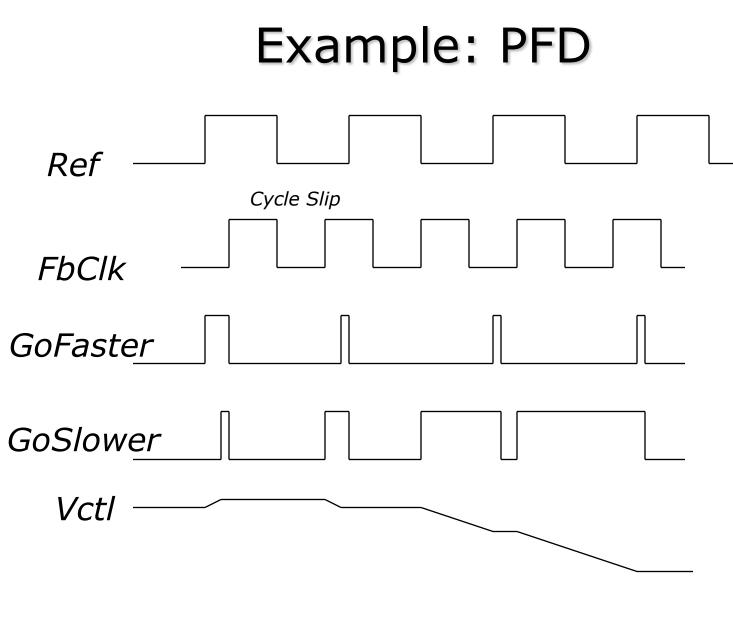

### PLL Circuit Diagram

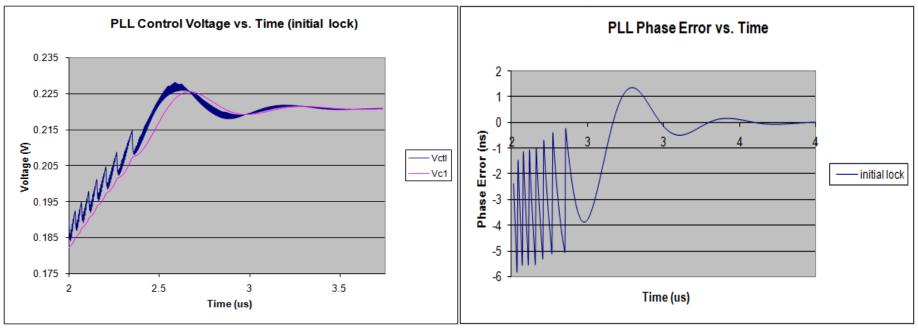

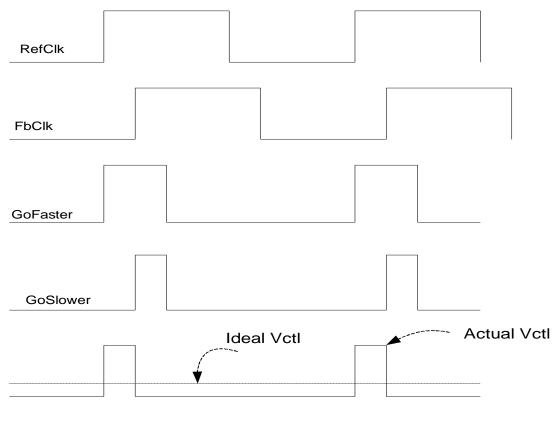

- Observations

- Under-damped PLL ringing

- Effect of cycle slips on Vctl

- Net integrating cap voltage Vc1 lags control voltage Vctl

### Components in a Nutshell

- Phase-Frequency Detector (PFD): outputs digital pulse whose width is proportional to sampled phase error

- Charge Pump (CP): converts digital error pulse to analog error current

- Loop Filter (LPF): integrates (and low-pass filters in continuous time) the error current to generate VCO control voltage

- VCO: low-swing oscillator with frequency proportional to control voltage

- Level Shifter (LS): amplifies VCO levels to full-swing

- Feedback Divider (FBDIV): divides VCO clock to generate FBCLK clock for phase comparison w/reference

# PLL Feedback Loop Theory

Copyright, Dennis Fischette, 2009

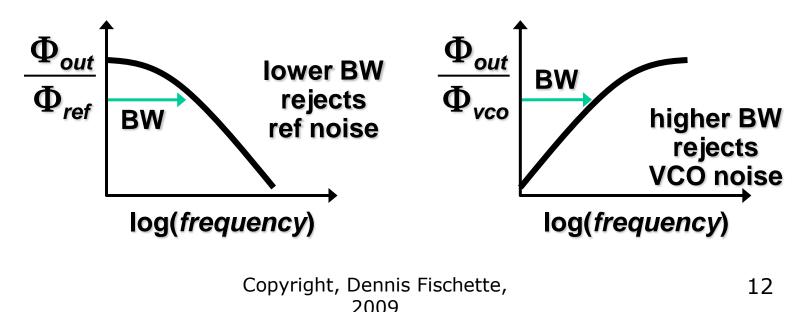

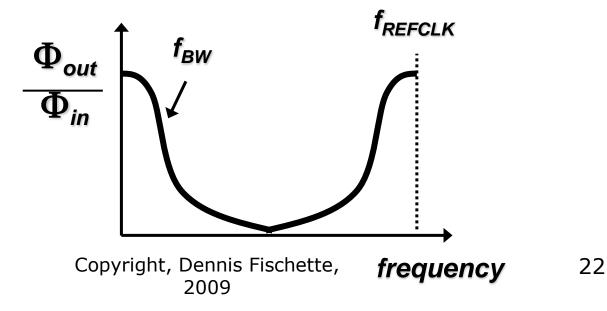

### What Does PLL Bandwidth Mean?

- PLL acts as a low-pass filter with respect to the reference modulation. High-frequency reference jitter is rejected

- Low-frequency reference modulation (e.g., spread-spectrum clocking) is passed to the VCO clock

- PLL acts as a high-pass filter with respect to VCO jitter

- "Bandwidth" is the modulation frequency at which the PLL begins to lose lock with the changing reference (-3dB)

### **Closed-Loop PLL Transfer Function**

- Transfer function describes how PLL responds to "excess" reference phase. i.e. RefClk phase modulation

- Analyze PLL feedback in frequency-domain

- *Phase* is state variable, not frequency

- "s" is the reference modulation frequency, not reference oscillation frequency

- Assumes continuous-time (not sampled) behavior

- $\phi_{fb} = (\phi_{ref} \phi_{fb}) * G(s)$  where G(s) == open-loop gain

- $H(s) = \phi_{fb}/\phi_{ref} = G(s)/(1+G(s))$

### **Open-Loop PLL Gain**

- $G(s) = (K_{vco}/s)I_{cp}F(s)*e^{-sTd}/M$

- where  $\phi_{err}$

- $K_{vco} = VCO$  gain in Hz/V

- $I_{cp}$  = charge pump current in Amps

- F(s) = loop filter transfer function in Volt/Amp

- M = feedback divisor

- $T_d$  = delay in feedback-loop (e.g. FBDIV, Tpfd/2)

### PLL Components in Frequency Domain

### **Closed-loop PLL Transfer Function**

•  $H(s) = \varpi_n^2 (1 + s/\varpi_z) / (s^2 + 2s\zeta \varpi_n + \varpi_n^2)$

- where

- $\varpi_n$  = undamped natural frequency (rad/s)

- $\varpi_z$  = stabilizing zero = 1 /RC<sub>1</sub> (rad/s)

- $\zeta$  = damping factor

- 2<sup>nd</sup>-order (two poles p1,p2 and one zero)

- $2^{nd}$ -order ignores  $C_2$  cap and feedback delays

- If  $\zeta < 1$ , complex poles lead to damped oscillation

- Real  $\rightarrow$  exponential decay( $\zeta \varpi_n$ ), Imag  $\rightarrow$  oscillation ( $\varpi_n$ )

- If  $\zeta > 1$ , z and p1 cancel: BW(-3dB) ~  $2\zeta \varpi_n$

- Acts like single-pole system

### What is a "Zero"?

• The "Zero" in the numerator of the closed-loop transfer function is the frequency in radians/s where the gain of the integral and proportional paths are equal.

⊥ Z = 1/sC

• Classic loop:

$$\varpi_z = 1 / RC_1$$

(rad/s)

Concept can be applied to loop filters that do not contain a resistor.

### Natural Frequency

Related to bandwidth

-  $\varpi_n = (2\pi * BW) / sqrt(1+2\zeta^2+sqrt((1+2\zeta^2)^2+1)))$

- Undamped Natural Frequency:

- $\varpi_n = \text{sqrt}(K_{vco}*I_{cp}/(M*C_1))$  in rad/sec

- where

- $K_{vco}$  = VCO gain in **Hz/V**

- $I_{cp}$  = charge pump current in Amps

- M = feedback divisor

- $C_1 = \text{large LPF capacitor}$

- For stability:  $\varpi_n/2\pi < \sim 1/15$  reference frequency

- Typical value: 500 kHz <  $\varpi_n/2\pi$  < 10MHz

#### **Damping Factor**

- Related to stability

- Damping Factor:  $\zeta = R_{lpf} * C_1 * \varpi_n / 2$

- Dimensionless, Usually  $\sim 0.45 < \zeta < \sim 2$

- Lower end of range for low period jitter

- Higher end of range for accurate ref phase tracking

- R<sub>lpf</sub> provides means to set stability independent of bandwidth

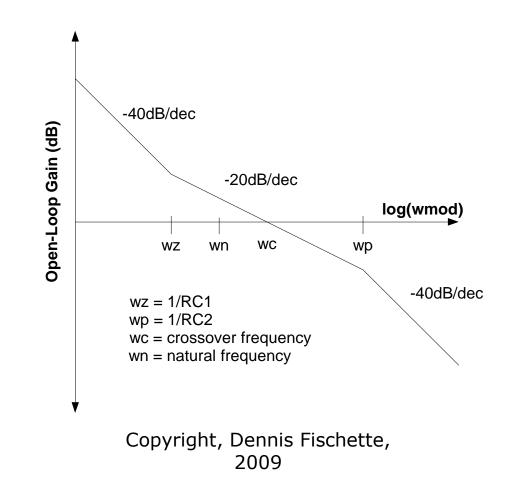

### **Open-Loop Transfer Function**

- 20\*log(Gain) vs. log(Modulation Frequency)

- 2 poles @ origin, 1 zero @ wz, 1 pole @wp

#### Stability and Phase Margin

- Phase margin determines stability as in other feedback loops  $\rightarrow 180$  phase of open-loop transfer function at crossover frequency

- $\phi_{m}$  (degrees) =  $(180/\pi)^{*}(atan(\varpi_{c}^{*}RC_{1})-atan(\varpi_{c}^{*}RC_{2})-\varpi_{c}^{*}T_{dly})$

- $\varpi_c ==$  crossover frequency

- frequency where open-loop gain G(s) = 0dB

- For stability:  $1/RC_1$  (zero) <  $\varpi_c$  <  $1/RC_2$  (parasitic pole)

- Typical Range:  $1.2^* \varpi_n < \varpi_c < 2.5^* \varpi_n$

- Phase margin ( $\phi_m$ ) ~ 100 \*  $\zeta$  (for  $\zeta$  < 0.5)

- Usually 45° < PM < 70°</li>

### Aliasing in a Sampled Loop

- Sampling nature of PFD  $\rightarrow$  frequency-domain aliasing

- Can't low-pass filter ref noise before PFD sampling unlike A/D's

- Need z-domain analysis for accurate PLL modeling analogous to sample-and-hold

- Phase of modulation with respect to ref affects aliasing

- e.g. ref modulation at  $\frac{1}{2} * f_{ref}$ . No jitter if sampled at 0°,180°, max at 90°,270°

- Modulation at frequencies > Nyquist  $(f_{ref}/2)$  appears at other frequencies

- e.g.  $f_{ref}$ =100MHz → ref modulation at 99MHz looks just like 1MHz ref modulation to the PLL

- continuous-time model says that PLL should reject more 99MHz noise than 1 MHz noise

## PLL Response to Reference Modulation

Copyright, Dennis Fischette, 2009

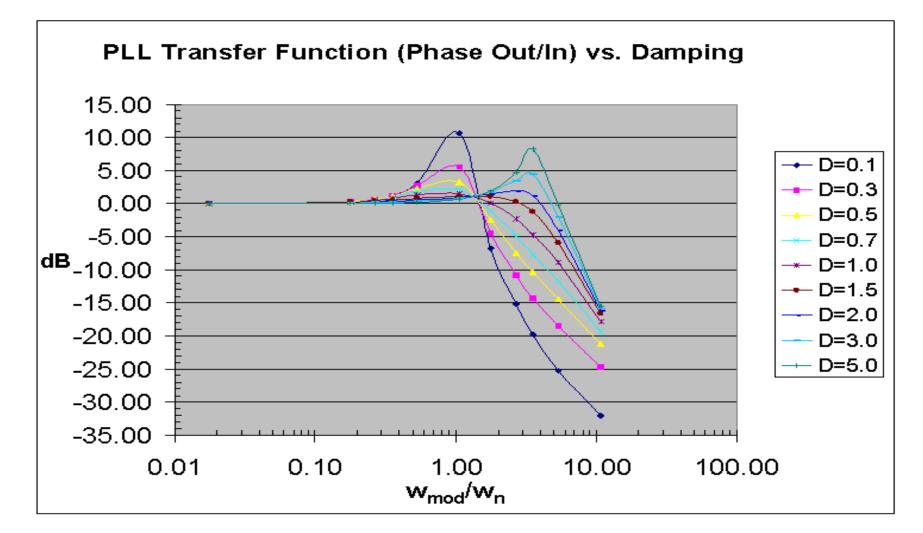

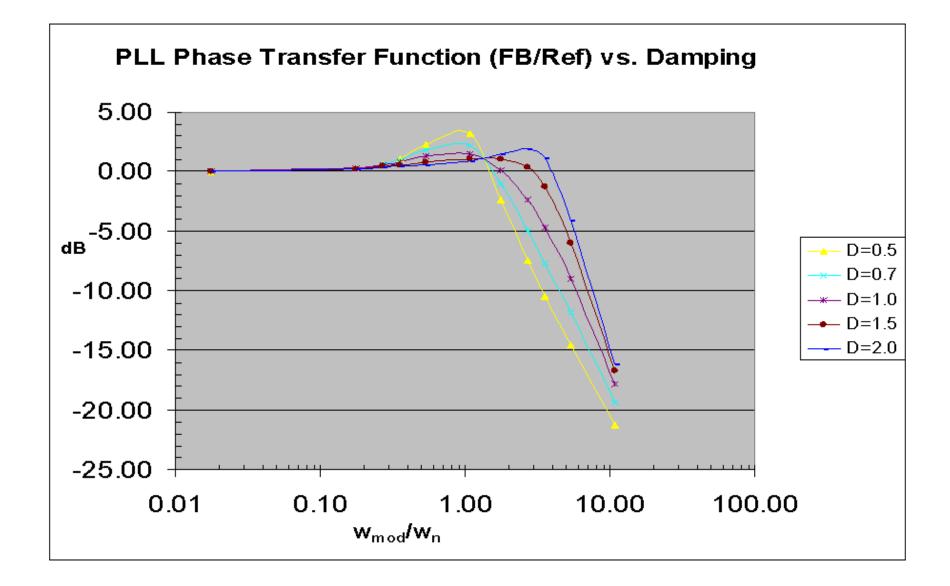

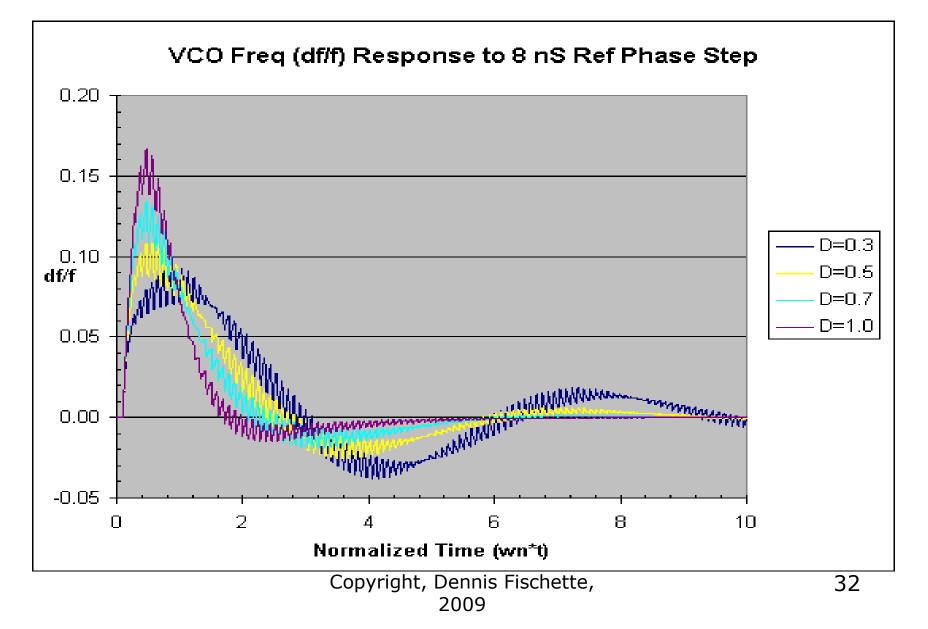

### Phase Tracking vs. Damping

- Phase Tracking vs. Damping

- Closed-loop Transfer Function ( $\phi_{fb}/\phi_{ref}$ )

- Phase Tracking → think "accumulated" period jitter or phase error

- Peaking at low and high damping factors  $\rightarrow$  bad

- Peaking at high damping due to smoothing capacitor pole  $(1/RC_2)$  and/or under-sampling (Gardner)

- Peaking very sensitive to parasitic pole  $(1/RC_2)$  at high R

- Min peaking w/damping ~ 1.0 1.5 if C\_2 ~ 5% \* C\_1

- Typical peaking: 1 3 dB (CPU high-end, IO low-end)

- For lower peaking, damping > 2 and  $C_2$  small

- Simulation Condition (following slides):  $C_2 = 6.7\% * C_1$

### **Closed-loop Transfer Function**

#### Copyright, Dennis Fischette, 2009

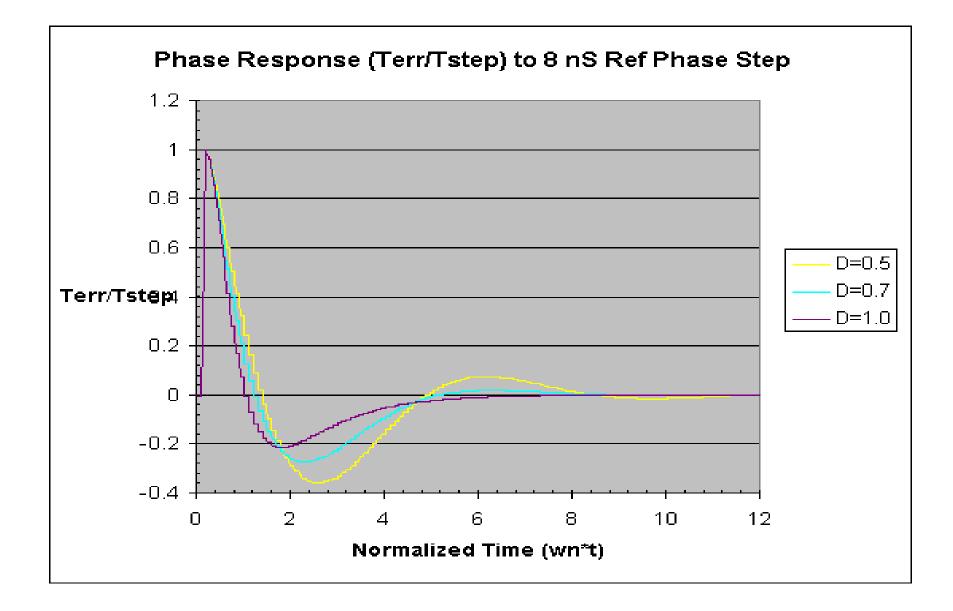

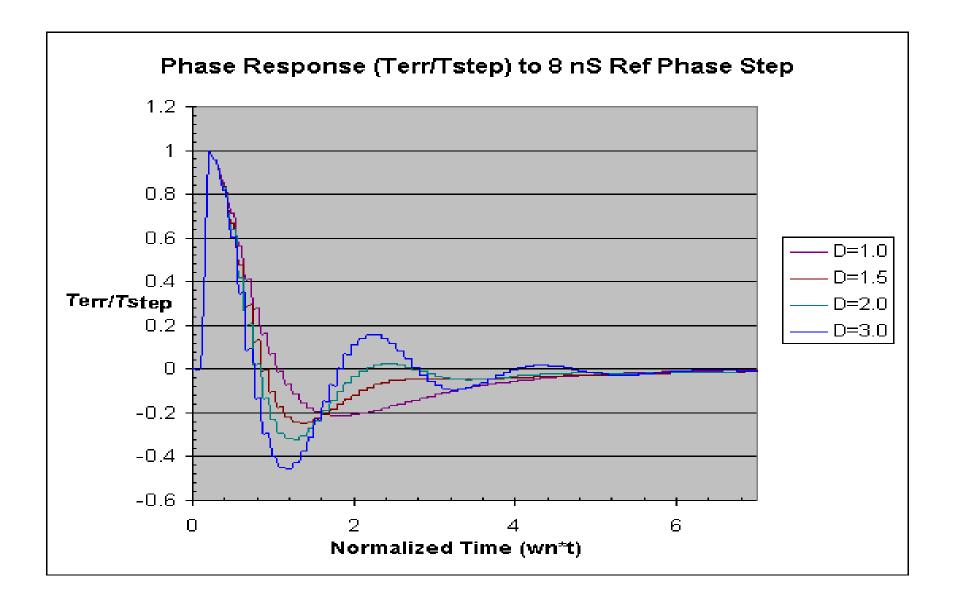

#### Phase Response to Ref Step

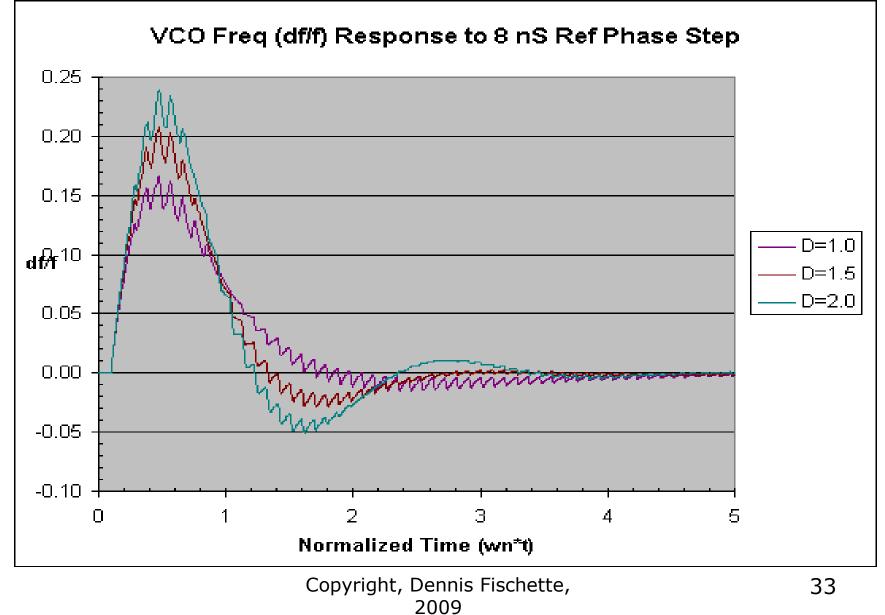

### Time-Domain Phase Response to Reference Step

- Transient Simulation Conditions (behavioral model):

- step reference phase by  $2\pi$  radians. Observe phase overshoot

- $C_2 = 10\% * C_1$  (high end of  $C_2$  range requires lower  $\zeta$ )

- Less ringing and overshoot as  $\zeta \rightarrow 1$

- Severe under-damping  $\rightarrow$  slow ringing and overshoot

- Severe over-damping  $\rightarrow$  fast ringing and overshoot

- Ringing at high damping due to smoothing pole (large RC<sub>2</sub>) and/or low over-sampling

### Time-Domain Phase Response to Reference Step

- From Gardner "Phaselock Techniques, 3<sup>rd</sup> Ed." (p. 102) ignores parasitic poles and over-sampling rate

- $\zeta < 1$ Terr = Tstep \* [(cos( sqrt(1- $\zeta^2$ )\* $\varpi_n$ t ) - ( $\zeta$ /sqrt(1- $\zeta^2$ )\*sin( sqrt(1- $\zeta^2$ )\* $\varpi_n$ t )] \* e<sup>- $\zeta \varpi n$ t</sup>

•

$$\zeta = 1$$

Terr = Tstep \* (1- $\varpi_n t$ ) \* e<sup>- $\varpi nt$</sup>

•

$$\zeta > 1$$

Terr = Tstep \* [(cosh( sqrt( $\zeta^2 - 1$ )\* $\varpi_n t$ ) - ( $\zeta$ /sqrt( $\zeta^2 - 1$ )\*sinh( sqrt( $\zeta^2 - 1$ )\* $\varpi_n t$ )] \* e<sup>- $\zeta \varpi n t$</sup>

#### Frequency Response to Ref Step

### Freq Overshoot from Ref Step

## **PLL Circuits**

- Phase-Frequency Detector

- Charge-Pump

- Loop Filter

- Voltage-Controlled Oscillator

- Level-Shifter

- Feedback Divider

- Voltage Regulator

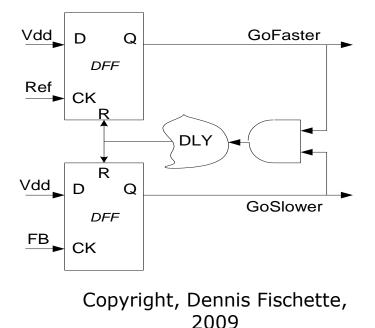

### Phase-Frequency Detector(PFD)

Copyright, Dennis Fischette, 2009

### **PFD Block Diagram**

- Edge-triggered

- Input duty-cycle doesn't matter

- Frequency correction takes precedence over phase correction no harmonic locking – 3 state operation

- Output pulse-widths proportional to phase error

- Reset delay to provide minWidth on output pulses to avoid "dead-zone"

- Symmetric NAND used to balance equalize delays from both inputs

- PFD fails as  $T_{reset}$  approaches  $T_{ref} \rightarrow limit$  cycles

- Challenge for Gb/sec IO links

- Pulsed-flop designs can be faster

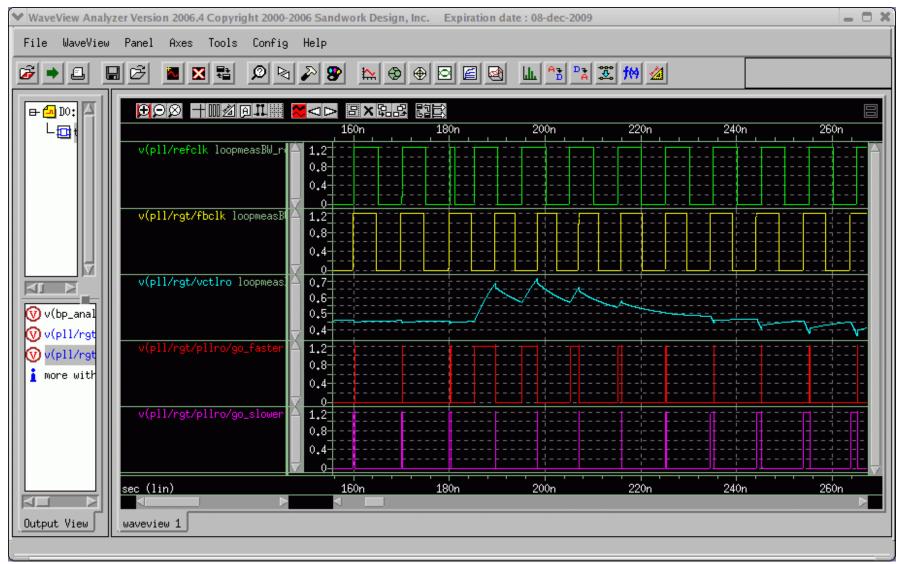

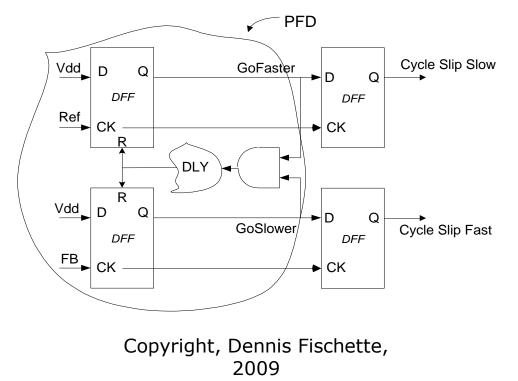

## **Frequency Lock Detector**

- Sample PFD GoFaster signal with rising RefClk

- Sample PFD GoSlower signal with rising Fbclk

- If either sampled signal is TRUE, then PFD detected two consecutive RefClk's or FbClk's → cycle slip and loss of frequency lock

- May apply "sticky bit" to result to capture temporary loss of lock

- Sample GoFaster/GoSlower with falling edges of RefClk/Fbclk to detect 180 degrees phase error

# Charge Pump(CP)

Copyright, Dennis Fischette, 2009

# Charge-Pump Wish List

- Equal UP/DOWN currents over entire control voltage range reduce static phase error

- Minimize mismatch caused by finite current sources  ${\rm g}_{\rm ds}$  and  ${\rm V}_{\rm t}$  mismatches

- $\Delta V_t \sim 1 / \text{sqrt}(W^*L)$

- long L in current sources for higher  $r_{\text{out}}$

- Stacked (a.k.a. common) gates in  $I_{sources}$  reduce mismatch

- use replica-bias CP and feedback amplifier to balance  $\rm I_{up}/I_{down}$  beware of mismatch between two CP cells

- increase in CP's phase noise due to finite BW of this feedback?

- Minimal coupling to control voltage during switching and leakage when off - reduce jitter and phase drift

- Insensitive to power-supply noise and process variations loop stability

# Charge-Pump Wish List

- Minimize coupling caused by "clock feedthrough" (C $_{\rm gd}$ ) and charge-injection big problem

- 1/2 sized dummy switches to reduce charge-injection

•  $Q_{inj} \sim \frac{1}{2} * C_{ox} * (W*L) * (V_{gs} - V_t)$

- Small (and/or limited swing) switches to reduce clock feedthrough – watch for leakage with limited-swing

- Balance timing and slew rates of Up/Down inputs

- Reduce PFD pulse-width to minimize device noise while still avoiding dead-zone (< 100 ps possible in 65nm) – noise is band-pass filtered by PLL

- Typical Icp: 5 $\mu$ A (mismatch)< I<sub>cp</sub> < 300  $\mu$ A (headroom)

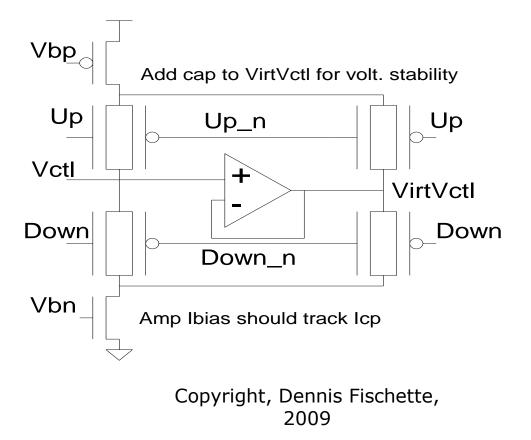

# Charge Pump: const I with amp

- Amp keeps V<sub>ds</sub> of current sources constant (Young '92), sinking "waste" current when UP and/or DOWN off

- $V_{offset}$  (off) → need high-gain amp

- −  $V_{offset}$  (on)=  $I_{cp}/g_m$  → often  $I_{amp}$  > 3-5X  $I_{cp}$  to reduce offset

- Both PMOS and NMOS input pairs needed for wide input range

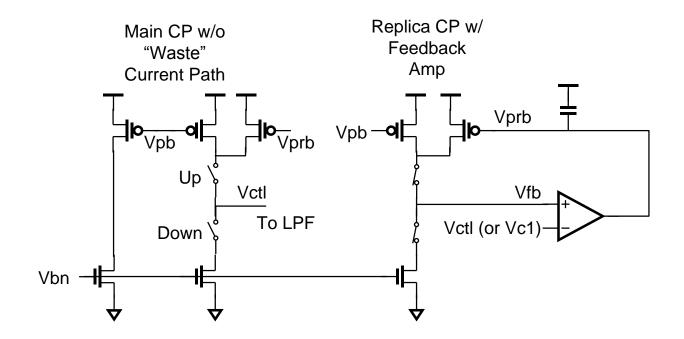

# Charge Pump: replica-feedback

- Replica-bias CP and additional amp used to set bias  $V_{\rm bp},$  forcing  $I_{\rm up}{=}I_{\rm dn}$  at low freq

- Start-up may be needed. Stability a concern

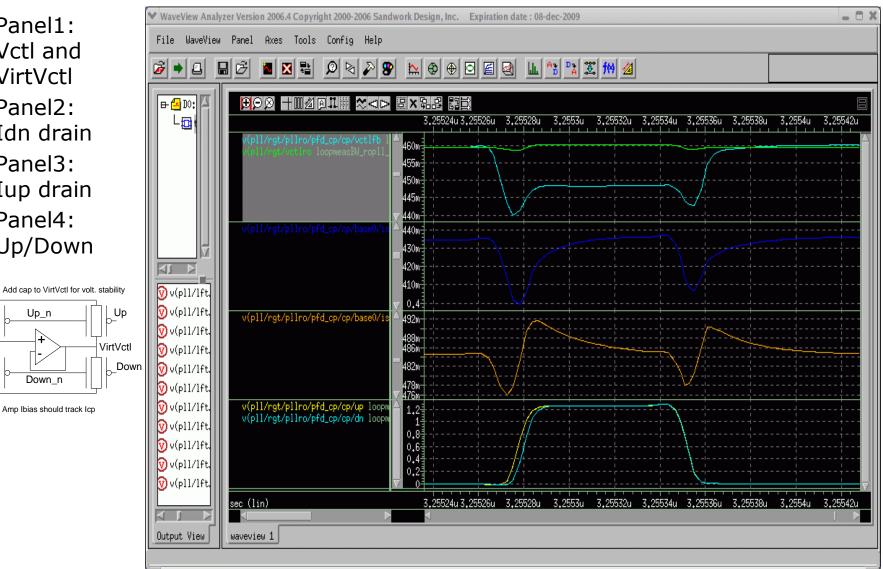

# Charge-Pump Switching

- Panel1: Vctl and VirtVctl

- Panel2: • Idn drain

- Panel3: • Iup drain

- Panel4: Up/Down

Up\_n

Down n

Vbp\_

Up

Vctl

Down

Vbn

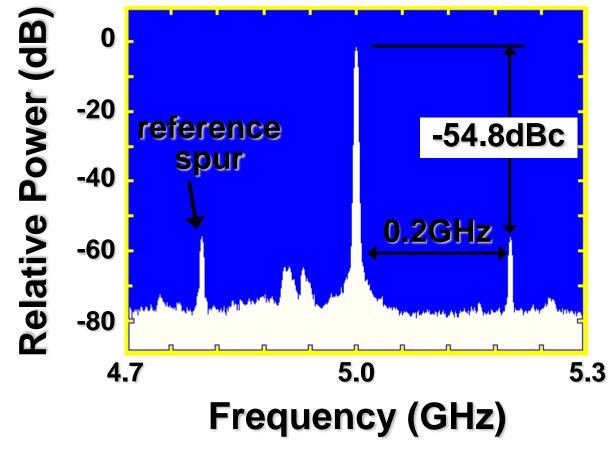

## Spectral Analysis of VCO Clock

• 5GHz VCO clock with 200MHz reference clock

#### Static Phase Error

- Causes: CP Up/Dn mismatch and/or control voltage leakage

- Jitter @ T<sub>ref</sub> (reference spurs) leakage more serious

- In lock, net control voltage currents must integrate to zero

- Mismatch example: if UP current is 2× larger, then DOWN current source must be on 2× as long to compensate and so feedback clock must lead reference for DOWN to be on longer

- $T_{err} = T_{dn} T_{up} = T_{reset} * (I_{up}/I_{dn} 1)$

- Medium-narrow reset pulse  $\rightarrow$  generally lower static error

- Leakage example: if  $T_{\rm ref}$  = 10ns,  $I_{\rm leak}$  = 0.1uA,  $I_{\rm cp}$  = 10uA

-

$$T_{err} = T_{ref} * I_{leak} / I_{cp} = 100 ps$$

• Typical static phase error < 100ps

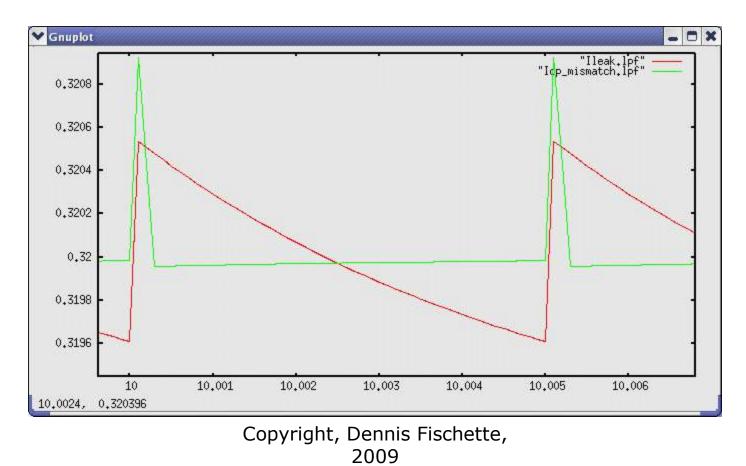

#### Static Phase Error

- "Green" Up/Down Mismatch, "Red" Leakage

- 100 ps static phase error in both cases

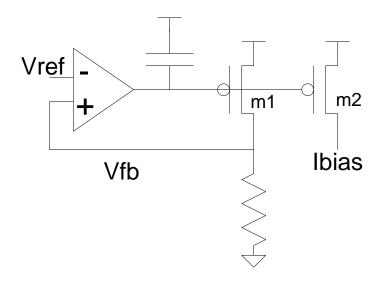

#### Bandgap-based I<sub>bias</sub>

- $I_b \sim V_{ref} / R$

- V<sub>ref</sub> generated from PVT-insensitive bandgap reference

- Con: feedback loop may oscillate

- capacitor added to improve stability

- resistor in series w/cap provides stabilizing zero (not shown)

- Pro: VDD-independent, mostly Temp independent

- Pro: Icp\*Rlpf = constant  $\rightarrow$  less PVT-sensitive loop dynamics

Copyright, Dennis Fischette, 2009

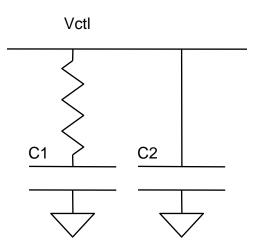

# Low-Pass Loop Filter (LPF)

## Loop Filter Basics

- Simplest and most commonly-used loop filter is continuous-time, passive filter (1 R, 2 C's) – affects stability and bandwidth

- Integrates low-frequency phase errors onto C1 cap to set avg. freq

- Resistor provides a means of isolating phase correction from frequency correction  $I_{\rm cp}*R_{\rm lpf}$  for stability but R adds thermal noise that is band-pass filtered by PLL

- C<sub>2</sub> cap filters high-freq noise spurs caused by sampling but adds parasitic pole at  $1/\mathrm{RC}_2$

- Other options include digital(FSM-based) filter, sampled-time filter (see Maneatis, Maxim), and continuous-time active filter

- Differential designs can reduce sensitivity to VDD and substrate noise and often area by  $2\times$ . Requires common-mode feedback loop

#### Loop Filter Resistor

- Resistance may be programmable using switches

- Parasitic switch resistance varies with control voltage

- Usually lowest at Vctl extremes if CMOS transmission gate

- Large Rswitch variation vs. Vctl if NMOS or PMOS only

- Usually Rswitch < 5-10% of Rlpf</li>

- Minimize gate leakage and noise coupling from switches

- Coupling less of a problem if using voltage regulators

- Typical values:  $500\Omega < R_{lpf} < 50k$

- Poly, Diffusion, Nwell R's most common

- MOSFET R's sometimes used if R placed "below" C1 cap

- Constant Vgs needed

- Copyright, Dennis Fischette, 2009

51

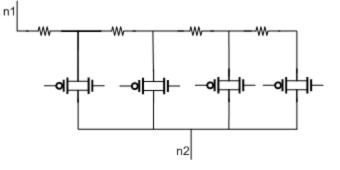

#### Integrating Cap Configuration

- Integrating cap (C1) may be placed "above" or "below" loop filter resistor

- Parasitic "bottom" capacitance for C1 "above" configuration

- Variable resistance if switches used in programmable resistor for C1 "below" configuration

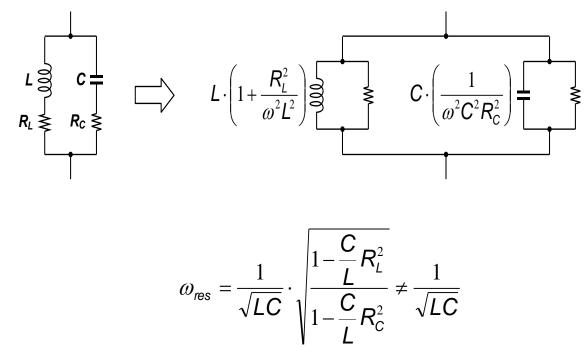

#### Loop Filter Capacitors

- Reference capacitor to same supply as VCO V-to-I reference → makes power supply noise common mode

- Gate Leakage in MOSFET caps can be a HUGE problem

- Exponential I<sub>leak</sub> vs. V: I<sub>leak</sub>~V<sub>gate</sub><sup>4</sup> (approximate)

- Weak temperature dependence

- −  $I_{leak}$  vs.  $t_{ox} \rightarrow \sim 2-3 \times$  per Angström

- Use metal caps (2-10X larger) or thick-gate (IO) oxide caps to minimize leakage

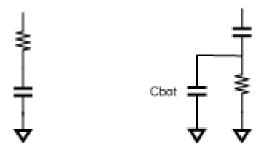

- If MOSFET caps, *accumulation* mode preferred flatter C<sub>gate</sub> vs. V

- $I_{leak}$  causes large refclk spurs (jitter) and static phase error

- Typical values:

- $5pF < C_1 < 200 pF$

- 1% (low phase error) <  $C_2/C_1$  < 10% (low period jitter)

- Smaller C<sub>1</sub> caps are becoming more common w/ higher reference frequencies and metal cap usage

## Depletion-Mode MOSFET C<sub>gate</sub> vs. V

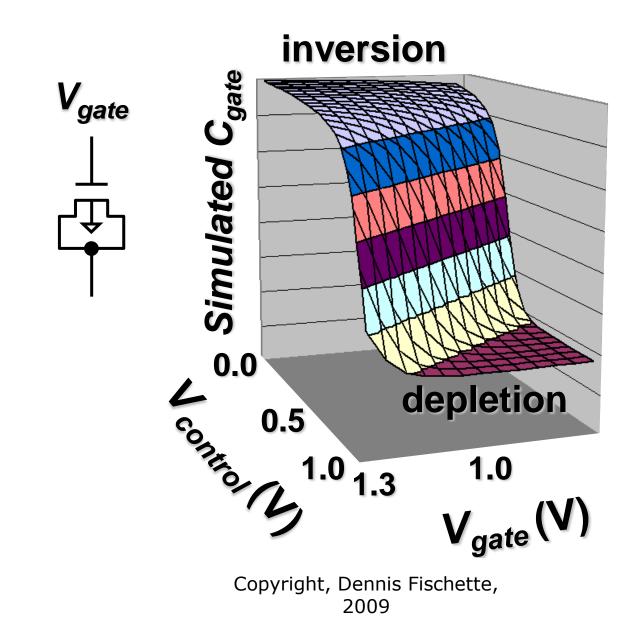

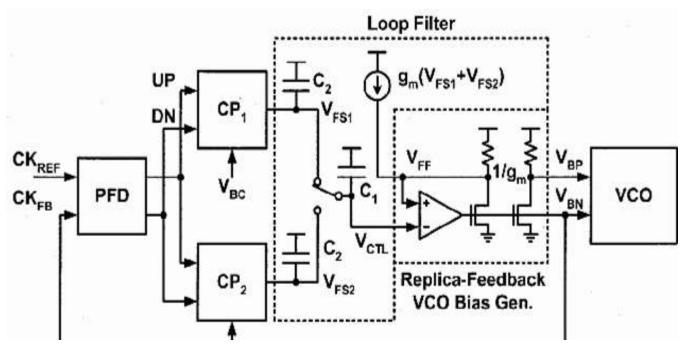

# Feed-Forward Zero: eliminate R

- Resistor in classic LPF provides an instantaneous IR on the control voltage causing the VCO V2I to generate a current bump on the oscillator input

- Alternative: eliminate R  $\rightarrow$  Add parallel CP path into V2I.

- requires parasitic cap ( $C_2$  not shown) to the proportional loop to reduce reference spurs

- see Maneatis '96 for continuous time or '03 for sampled loop filter

- Reduces LPF phase noise? Commonly used in low phase-noise I/O apps.

# Dual-Loop Charge-Pump Mismatch

- Iup/Idown ratios in proportional and integral charge-pumps are partly uncorrelated due to random device mismatch

- Net charge from integral CP must integrate to zero for stable frequency – determines static phase error alone

- Net charge from proportional CP causes frequency kick every PFD cycle (Kvco\*I\*R) caused by static error and its own Iup/Idown mismatch

- Upshot: control voltage adjusts up or down from ideal level to achieve correct average frequency but f<sub>VCO</sub> varies within PFD cycle (phase wander) – need well-matched CP's to avoid this effect

# Dual-Loop Charge-Pump Mismatch

Static error in integral charge-pump →period jitter and phase wander

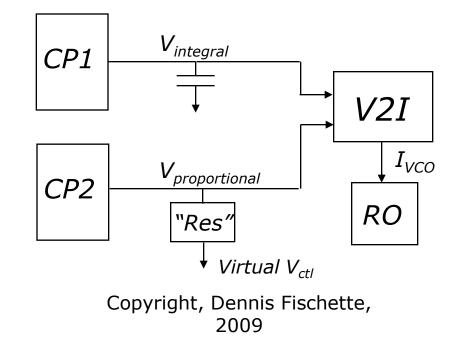

#### Sample-Reset Loop Filters

- Single charge-pump for  $I_{int}$  and  $I_{prop}$  Zero ~ sqrt(C1/C2)

- e.g. Maneatis (JSSC '03)

- Two charge-pumps to allow for reset (discharge) delay

- Spreads phase correction over Tref can reduce ref spurs

- Mismatch between CP's  $\rightarrow$  significant VCO phase modulation at f<sub>ref</sub>/2

# Voltage-Controlled Oscillator (VCO)

Copyright, Dennis Fischette, 2009

# Voltage-Controlled Oscillator

- Ring-oscillator (RO)

- Wide frequency range

- Easy to design, integrate, and model

- Easy to generate multi-phase outputs

- Small area but high power for low jitter

- Low Q higher jitter

- LC-tank

- Narrow frequency range

- Need field-solver tools to model inductor and accurate varactor model

- Hard to generate multi-phase outputs

- Large area but low power

- High Q lower jitter

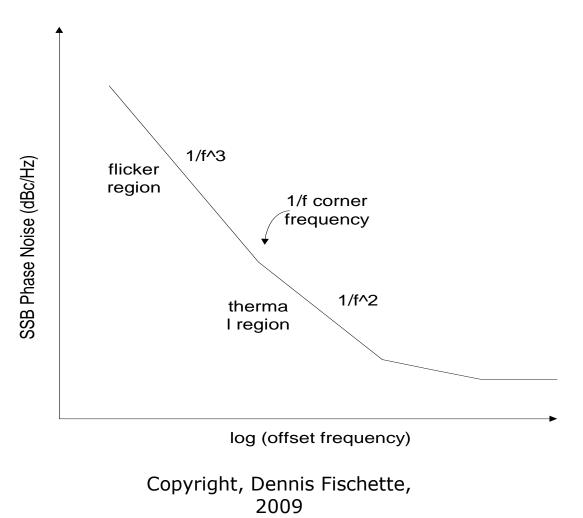

## Single-Sideband Phase Noise Plot

• Open-loop VCO

# **Open-Loop VCO Phase Noise**

- Measured vs. offset frequency (f) from carrier

- Spectral Density of Phase Fluctuations  $(S\phi(f))$

- $S\phi(f) = 2L(f)$

- L(f) is Single-Sideband Phase Noise (dBc/Hz)

- Analogous to Power(sideband)/Power(carrier)

- S\u03c6(f) ~ 1 / f<sup>2</sup>

- thermal region, mid-to-high freq

- S\u03c6(f) ~ 1 / f<sup>3</sup>

- flicker region, low freq

- Flicker noise mostly filtered by high BW PLL

## VCO Phase Noise - Leeson

- $L(f) = 10 \log (FkT/A)*(1/8Q_{L}^{2})*(f_{osc}/f)^{2}$ ]

- F is the device noise factor at operating power level A

- k is Boltzmann's constant, 1.38e<sup>-23</sup> J/K

- T is temperature (K)

- A is oscillator output power (W)

- Q<sub>L</sub> is loaded Q (dimensionless)

- f<sub>osc</sub> is the oscillator carrier frequency

- f is the frequency offset from the carrier

- Valid:

- For offsets greater than the 1/f flicker corner frequency

- the noise factor at the operating power level is known

- the device operation is linear

- Q includes the effects of component losses, device loading and buffer loading

- Source: Analog Devices: AnalogDialogue

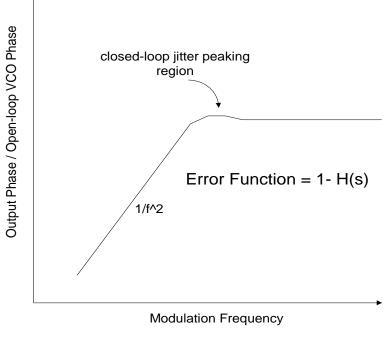

#### Open-loop → Closed-Loop Phase Noise

- Goal: determine how much open-loop VCO phase noise remains after applying PLL feedback loop

- Method: multiply VCO's open-loop single-sideband phase noise by square of PLL's "error function" <1- H(s)> where H(s) is closedloop transfer function

Copyright, Dennis Fischette, 2009

# VCO Noise Tracking: Phase Error vs. Bandwidth

- For random VCO noise (i.e. thermal):

- lower BW  $\rightarrow$  more accumulated phase error

- Why? More jittery VCO cycles before feedback loop can correct:

$$\phi_{error} \propto J_{RMS, period} \cdot \sqrt{\frac{\omega_{vco}}{\zeta \omega_n}}$$

where  $J_{rms}$  = open-loop VCO RMS period jitter

# PLL Suppression of VCO Noise

- PLL acts like a high-pass filter in allowing VCO noise to reach output

- Need noise-immune and low-intrinsic noise VCO to minimize jitter

- Feedback loop cannot react quickly.

- Tradeoff between tuning range & noise sensitivity

- Power-supply noise is usually largest source of VCO deterministic jitter(DJ) if no voltage regulator. Otherwise, largest jitter source is device noise (RJ).

- $\bullet$  VCO power-supply sensitivity should be at least 10-20× less than inverter

# PLL Suppression of VCO Noise

- For RO: high power, fast edges, large swing → lower device noise and lower random jitter (RJ)

- $J_{rms}$  (open-loop period) ~sqrt(kT/2NC) / ( $f_{vco}*V_{swing}$ )

- where N=#of stages, C=cap/stage

- Match rise/fall times, inter-stage delays to minimize phase noise (lowers ISF)

- RMS random jitter (*kT*) < 0.02% 0.2% VCO period (typical)

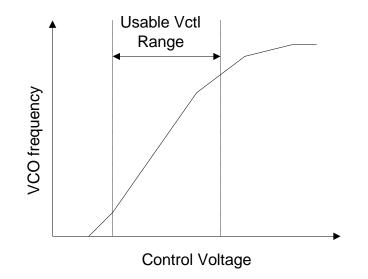

#### **RO VCO Gain**

- Typical VCO gain: K<sub>vco</sub> ~ 1-3× \* f<sub>max</sub>. May vary w/PVT by > 2×

- need frequency range: >2× to allow for PVT

- desire constant gain over most of usable control voltage range

- use digital calibration to reduce :  $K_{vco}$  variation

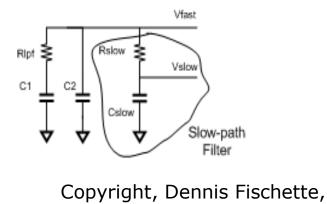

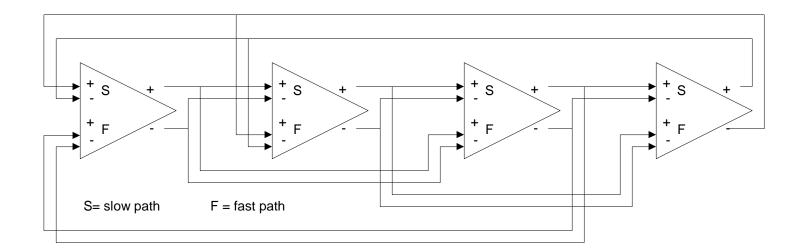

# Achieving Low RO VCO Gain

- Goal: low gain and wide frequency range→ allows for low PLL BW and/or can help filter charge-pump and resistor noise

- Make VCO frequency a function of TWO control paths

- Fast-path: low Kvco connect to normal loop filter path

- Slow-path: high Kvco connect to secondary control path with low BW (<< 1/10 PLL BW) – requires stable refclk frequency</li>

- Loop dynamics are determined mostly by fast-path model in H(s)

2009

- Slow-path RC filter added to normal loop filter

- Can connect  $R_{slow}$  to  $C_1$  cap instead of  $C_2$  cap.

- Add unity-gain buffer if V<sub>slow</sub> leakage is high

- Increases lock time w/o additional logic and switches

- Techniques to reduce lock-time can cause instability

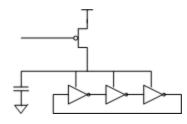

# Voltage-Controlled Oscillator

- Barkhausen criteria for sustained oscillation

- loop gain must exceed 1, loop phase must equal 360°

- more RO delay stages  $\rightarrow$  easier to initiate oscillation

- gain(DC) > 2 for 3 stages, gain > sqrt(2) for 4 stages

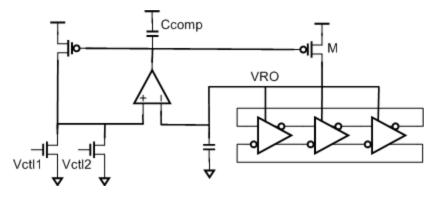

# VCO w/current-starved inverters(CSI)

- RO VCO usually consists of two circuits

- bias generator (e.g.  $V_{ctl}$  to  $I_{ctl}$ )

- voltage or current controlled ring oscillator (RO)

- Usually odd # of stages (usually 5+). Even # ok if differential RO

- Feedback INV  $\rightarrow$  usually weaker by > ~3-4×

- Tune frequency by adjusting "VDD" of inverters changes delay

- "Vdd" for inverters is regulated output of VCO V2I

Copyright, Dennis Fischette, 2009

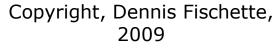

## Generic V-to-I for CSI RO

- Bias circuit for current-starved inverter-based RO. Start-up necessary.

- Feedback amplifier provides good low-freq power-supply rejection

- Caps to Vdd and Vss provide good high-freq rejection but add parasitic poles  $\rightarrow$  e.g.,  $\varpi_{p1} = 1/(R_{ro}*C_{vro})$ ,  $\varpi_{p2} = 1/(R_{amp}*C_{comp})$

- Programmable mirror-ratio (M) allows for programmable Kvco, wider frequency range, and lower phase noise

- Dual-control path: fast/slow LPF or feed-forward zero LPF

- Adding source-degeneration resistors to current sources may reduce device noise

- Stability disturb ckt w/narrow transient pulse FFT(delta function)  $\rightarrow$  white noise. Hard to model RO impedance in AC stability sims

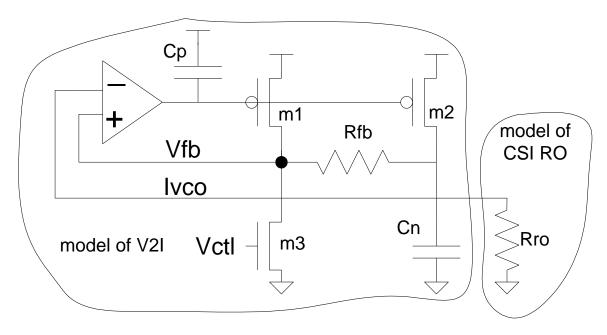

## V2I for CSI RO (V. von Kaenel (JSCC '96)

- Bias circuit for current-starved inverter-based ring oscillator

- Feedback  $\rightarrow$  amp provides good low-freq power-supply rejection

- Caps to Vdd and Vss provide good high-freq rejection but add parasitic poles  $\rightarrow$  e.g.,  $\varpi_p = 1/(R_{ro}^*C_n)$

- Start-up necessary. Stability a concern

Copyright, Dennis Fischette, 2009

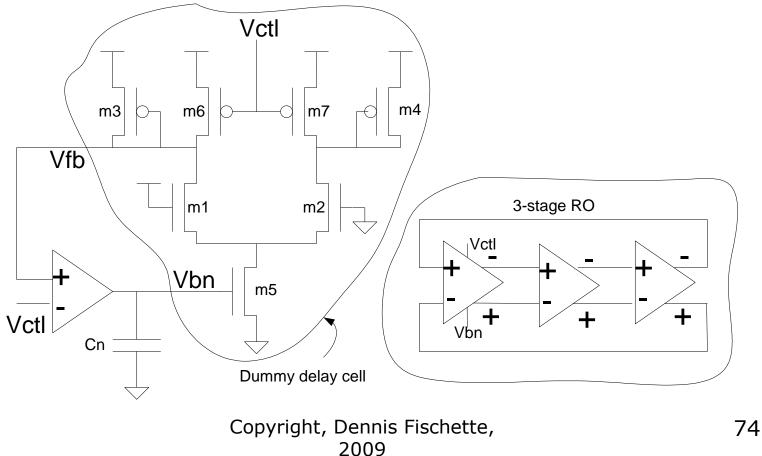

## Diff-Amp VCO w/Replica-Bias V2I

- $V_{swing} = V_{ctl}$  (Maneatis '96)

- Amp provides DC power-supply rejection

- Stable, but getting high BW and good PSRR tricky

- Start-up necessary

#### VCO w/Feed-Forward Path

- RO delay stage may receive inputs from multiple prior stages (e.g. N-1 and N-2)

- allows N-stage VCO to oscillate at speeds otherwise attainable only by reducing # of stages

- easier to implement with differential signals

- extra care must be taken to ensure that RO will safely oscillate

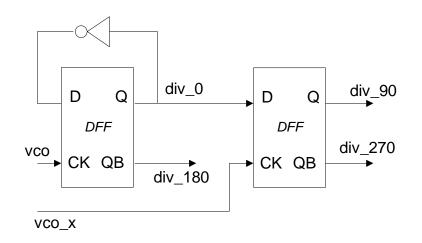

#### Quadrature Output Clocks

- Quadrature clocks (0°, 90°, 180°, 270°)

- requires 4 delay stages or

- divide "differential" VCO outputs by 2, then delay one set of divided outputs by  $\frac{1}{2} T_{vco}$  to generate quadratures. Allows any # of delay stages

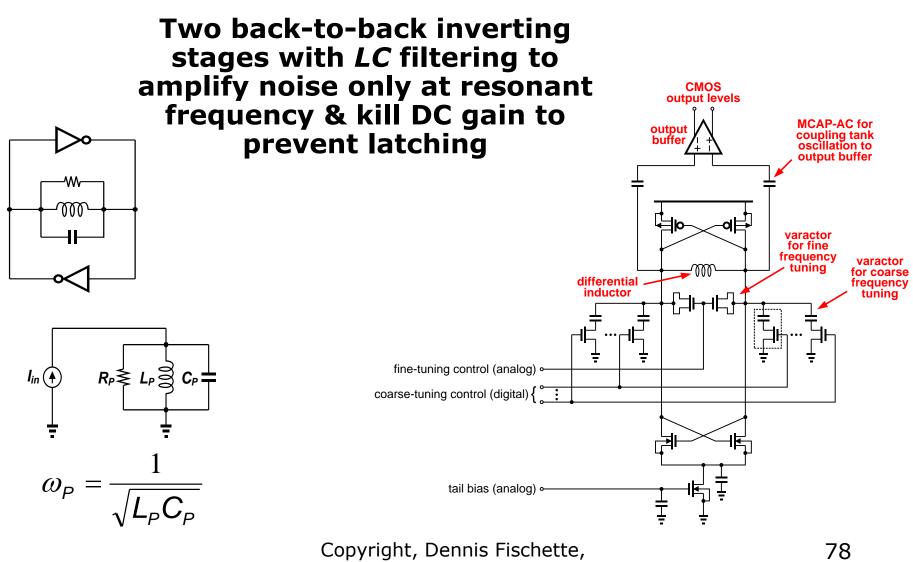

# LC VCO

#### • Pros

- Low jitter / phase noise performance

- If *L* & *C* are modeled correctly, frequency prediction is good

- Cons

- Limited tuning range

- Area (inductor)

- Inductor is a not supported at many companies

- Accurate varactor model is challenging

- Key design considerations

- Keeping noise sources quiet

- Varactor choices

- Tuning range vs. noise performance

- Oscillation amplitude control

#### LC VCO Schematic

2009

#### LC VCO

# LC VCO Design Concerns

- Thermal noise of parasitics tuning L & C parasitics

- Device noise of cross-coupled –gm devices (mostly thermal noise)

- 1/f noise of tail (upconverted to fundamental via mixer action)

- L needs to add dummy fingers to pass metal density rules

- Fingers oriented orthogonally to inductor turns to minimize parasitic eddy currents from magnetic coupling

- Fingers staggered between Mn & Mn+1 to reduce CMP topography

- Need symmetry in inductor underpass connections

- Need to account for high-frequency effects (proximity/skin effects, dielectric loss, etc.) in inductor

# Setting LC VCO Tailbias

- Tail biasing sets oscillator current

- Need enough current to create enough  $g_m$  in cross-coupled devices to overcome resistive losses in tank in order to start up initial oscillation and sustain oscillation

- Can set with static control or local amplitude-control loop

- Ramp tailbias down, i.e., slowly kill oscillator gain & check when oscillations die out (defined when peak swing falls below 0.1V)

## LC VCO Temperature Effects

Metal TCR affects oscillation frequency when inductor Q is limited

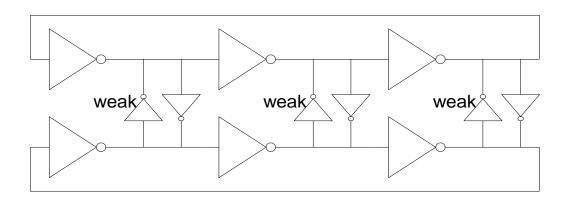

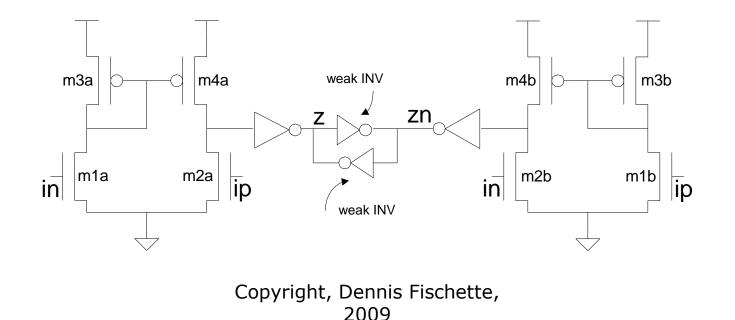

## VCO Level-Shifter

- Differential-pair without tail current

- Need sufficient gain at low VCO frequency use low-V<sub>t</sub> NMOS

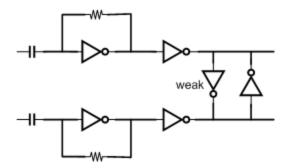

- Use NMOS input pair if VCO swing referenced to VSS for better power-supply rejection – often low Vt for wider input range

- For best duty-cycle, use two instances of level-shifter (swap inputs), and couple complementary outputs with weak inverters

- Typical duty cycle:  $50 \pm 3\%$  with random mismatch

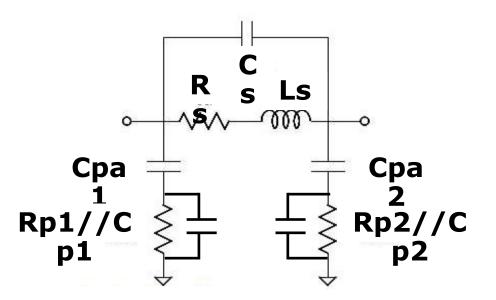

## AC-Coupled VCO Level-Shifter

- Can't pass low-frequency clock due to AC-coupling

- Caps decouple VCO common-mode from level-shifter input common-mode

- Large resistors bias input inverters at trip-point w/o attenuating gain

- Parasitic capacitance at input of first inverters attenuates AC signal

- Typical duty cycle:  $50 \pm 3\%$  with random mismatch

Copyright, Dennis Fischette, 2009

## Feedback Divider

Copyright, Dennis Fischette, 2009

# Feedback Divider (FBDIV)

- Typical Implementation: programmable, synchronous digital counter

- Max FBDIV frequency should be greater than max VCO frequency to avoid "run-away" - beware of Synthesized, Placed & Routed designs

- Counter output may glitch  $\rightarrow$  re-sample with VCO output to clean up glitch, reduce latency and phase noise

- Loop Phase Margin Degradation ~  $\varpi_{c^*}T_{fbdly}$

- usually insignificant (a few degrees)

- Divider may be internal to PLL or after clock tree to cancel clock tree skew

- May provide additional output signals used to deterministically synchronize tester controls to VCO clock and/or walk signals between various on-chip clock domains

## Fractional-N Dividers

- Divide VCO clock by non-integer value to allow for finer frequency resolution

- Dual modulus: N, N+1

- Vary divisor from N to N+1 at various rates, duty-cycles to achieve intermediate value

- Requires delta-sigma modulation to reduce/re-shape noise spurs (move to higher frequency)

- PLL feedback loop filters high-frequency spurs

- Complementary Approach: multi-phase VCO outputs

- e.g. 8 or 10 output phases

- Feedback clock period can be adjusted by less than one VCO clock

- More power, lower fmax for multi-phase VCO

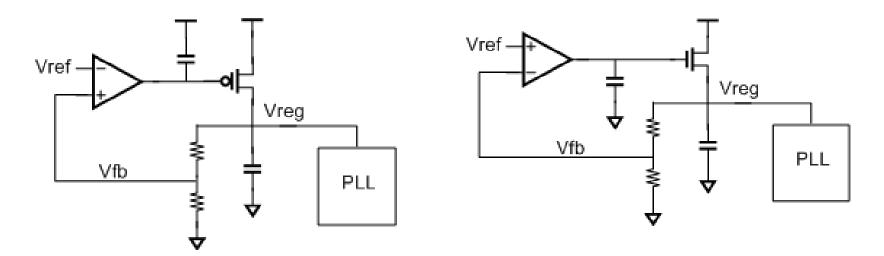

## Voltage Regulator

• Provides stable, PVT-insensitive, clean power-supply for PLL

- lower jitter, phase noise

- more stable loop dynamics, VCO range, etc.

- aim for > 30dB PSRR, definitely > 20dB

- Uses bandgap reference to set voltage and bias current levels

- Two voltage regulators sometimes used

- High VDD for charge-pump (analog) and lower VDD for VCO

- "Quiet" for analog (CP, VCO bias) and "Dirty" for digital (PFD, FBDIV)

## Voltage Regulator

- Requires higher power-supply (e.g.,  $1.8V \rightarrow 1.2V$ )

- Wastes current

- higher VDDA and bandgap/regulator over-head (0.5-3mA).

- aim for current overhead < 20%. <5% is achievable in some apps</li>

- Regulator area (inc. bandgap) is small compared to decoupling cap area

- Area (MOSFETs, Rpoly, diodes)  $\sim$  70 x 70  $\mu$ m<sup>2</sup> (65nm)

- Area (DECAPs) ~ 125 $\mu$ m x 125um for 100pF (65nm)

- Typical cap ~ 30-300pF

- V<sub>t</sub>-mismatch in bandgap amplifier input pair dominates overall regulator mismatch

- 3mV offset at amp  $\rightarrow \sim 20$ mV variation at output

- Goal < 25mV 1- $\sigma$  variation from device mismatch

- Goal < ±5mV PVT variation (due mostly to diodes)</li>

## Voltage Regulator

- Hard to stabilize over wide Iload and Cload ranges

- NMOS source-follower output stage

- Requires more headroom

- Faster response and easier to stabilize

- PMOS common-source output stage

- Can handle larger current loads  $\rightarrow$  larger Vgs

#### Digital PLL's

Copyright, Dennis Fischette, 2009

## What is a Digital PLL?

- Replace charge-pump (time error-to-charge) with TimeError-to-Digital Converter

- Replace loop filter with discrete-time digital filter (usually 2<sup>nd</sup> or 3<sup>rd</sup> order sigma-delta)

- Replace voltage-controlled VCO with digital-control (vary cap load, interpolation, etc.)

- Are analog components "allowed"? Voltage regulator? Analog current-steering DAC for VCO?

- Sampled-system modeled in the Z-domain

# Why a Digital PLL?

- Replaces process and noise-sensitive analog circuits with digital equivalents – advances on work with digital DLL's

- Increases PLL design portability and testability

- Takes advantage of area scaling with nm devices

- Greater flexibility in loop bandwidth don't need huge capacitors for low BW

- Increases ability to test and observe. e.g. open-loop, disturb loop

- Fast behavioral simulation

- "Good-enough" for frequency synthesis applications

- ISSCC presentations: TI('04) and IBM ('07)

# Why NOT a Digital PLL?

- Often not "good enough" for phase-tracking applications

- VCO frequency has finite frequency resolution (e.g. 10-14 bits). May use coarse DAC if high-frequency dithering available

- VCO has limited range requires range control and/or calibration

- VCO may have poor noise rejection if purely digital frequency control and no voltage regulator (usually analog)

# Why NOT a Digital PLL?

- Need high-frequency over-sampling clock for sigma-delta loop filter – VCO? Refclk? Start-up problem?

- TimeError-to-Digital Converter is hard poor resolution, high power – usually < 5 bits</li>

- Bang-bang is an alternative (IBM)

- FbDiv internal state contains phase error information

- Digital filter generates large noise spurs, possibly inducing jitter, and dissipates more power than passive loop filter

- Requires delta-sigma modulation to reduce spurs

- Generating proportional correction can be tricky

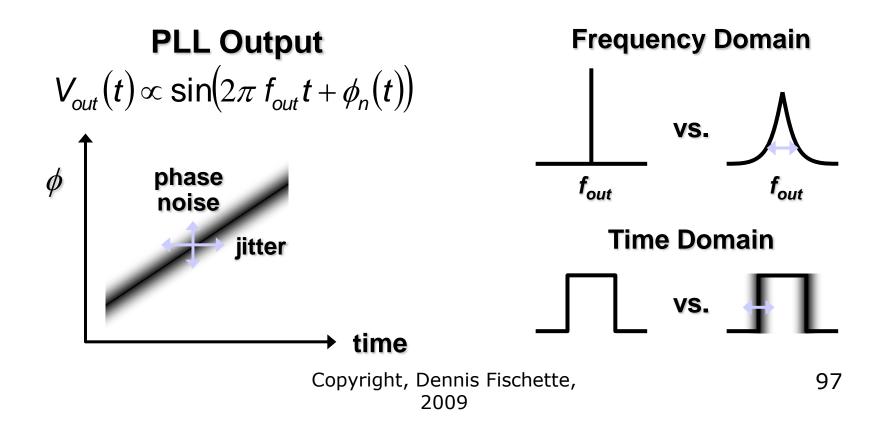

#### Phase Noise to Jitter

Copyright, Dennis Fischette, 2009

#### Phase Noise and Timing Jitter

- Phase Noise (frequency domain) ↔ Jitter (time domain)

- Noise is frequency-dependent with random & deterministic components

- VCO and loop filter resistor often largest sources of noise

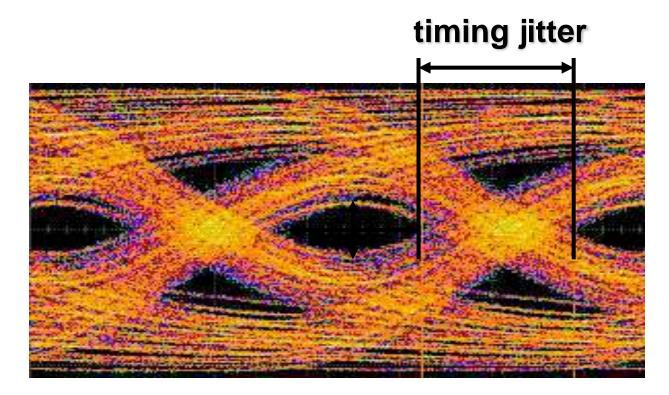

## Timing Jitter: Eye Diagram

- Example of timing jitter in serial link.

- Overlay scope traces of several bits on top of each other

## Jitter Definitions

- Phase Jitter (sec)

- deviation of VCO output edges from ideal placement in time.

- specified over a time interval or frequency range.

- important for I/O apps (e.g. PCI-Express < ±1.5ps RMS)</li>

- measure with spectrum analyzer or scope with jitter package

- Period Jitter (sec)

- deviation of VCO period from ideal period

- derivative of Phase Jitter with respect to time

- peak-to-peak period jitter  $(J_{pp})$  is max VCO period min VCO period

- most important for CPU-like apps

- e.g. 10-20ps for 2GHz CPU clock

- easily measured on scope self-triggered infinite-persistence or jitter package

- Cycle-to-Cycle Jitter (sec)

- change in VCO period from cycle N to cycle N+1

- derivative of Period Jitter with respect to time

- not important for CPU-like apps

#### Jitter Definitions

- TIE (sec)

- time difference between total of N-consecutive actual VCO cycles and N ideal cycles

- easily measured on oscilloscope with jitter package self-triggered measurement

- TIE "time-interval error"

#### **Noise Sources**

- Major internal PLL Noise Sources

- VCO oscillator(mostly thermal) very significant

- VCO bias (flicker and thermal) very significant

- Loop filter resistor (thermal)

- Charge-pump (flicker (1/f) and thermal)

- Flicker Noise

- $V_n^2 (V^2/Hz) = K_f / (C_{ox}^*W^*L^* f)$

- $K_f \sim 10e^{-24}$  PMOS often lower than NMOS

- Thermal Noise

- $I_n^2$  (Amp<sup>2</sup>/Hz) = 4kT\*g<sub>m</sub>\* $\gamma$

- $\Box~\gamma\sim$  2/3 for older CMOS technologies, much higher in deep submicron

- PLL feedback loop

- Low-pass filters ref and charge-pump noise

- Band-pass filters loop-filter resistor noise

- High-pass filters VCO noise (1-H(s))

## Converting Phase Noise to Jitter

• RMS Phase Jitter

$$J_{phase} = \frac{1}{2\pi f_{vco}} \sqrt{\int S_{\phi}(f) df}$$

- $S(f) \rightarrow 2^*L(f)$  where L(f) is single-sideband phase noise

- To convert to dBc/Hz, use 10log<sub>10</sub>(L(f))

- Easily measured using spectrum analyzer low noise floor

- Ideal reference is measurement trigger

- Integration range depends on application (e.g. PCIe: f<sub>min</sub> = 1.5MHz)

- usually stop integration at  $f_{\rm 0}/2$  to avoid capturing carrier and harmonics

- e.g., 5ps from 1MHz to  $f_0/2$  with BW=15MHz and 2.5GHz clock (SOI bad for phase jitter)

## **Converting Phase Noise to Jitter**

• RMS Period Jitter

$$J_{period} = \frac{1}{2\pi f_{vco}} \sqrt{8\int L(f)\sin^2\left(\frac{\pi f}{f_{vco}}\right)} df$$

Spectrum analyzer can't do this integral. Post-process phase noise

- e.g., J<sub>per</sub>~300fs w/2.5GHz clock

- Usually dominated by VCO bias and VCO?

- Spectrum analyzer usually has lower noise floor than scope (scope floor ~800fs @ 40Gsample/sec)

## **Converting Phase Noise to TIE**

• Time-Interval Error (TIE)

$$J_{TIE} = \frac{1}{2\pi f_{vco}} \sqrt{8 \int L(f) \sin^2(\pi f \tau) df}$$

- "*Tau"* is time interval over which phase drift is measured

- Spectrum analyzer can't do this integral. Post-process phase noise

- $J_{TIE} (Tau) = sqrt(2) * J_{phase}$  where  $Tau = 1/f_{start}$  and  $f_{start}$  is the starting frequency for both integrations

#### **Circuit Verification**

Copyright, Dennis Fischette, 2009

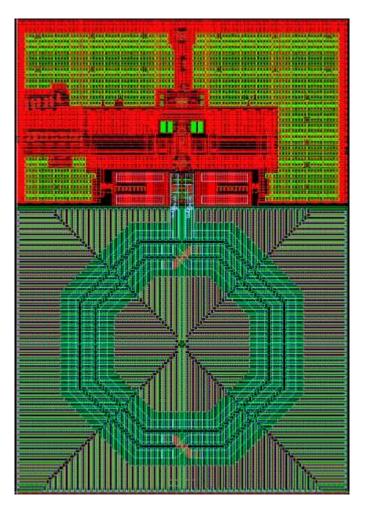

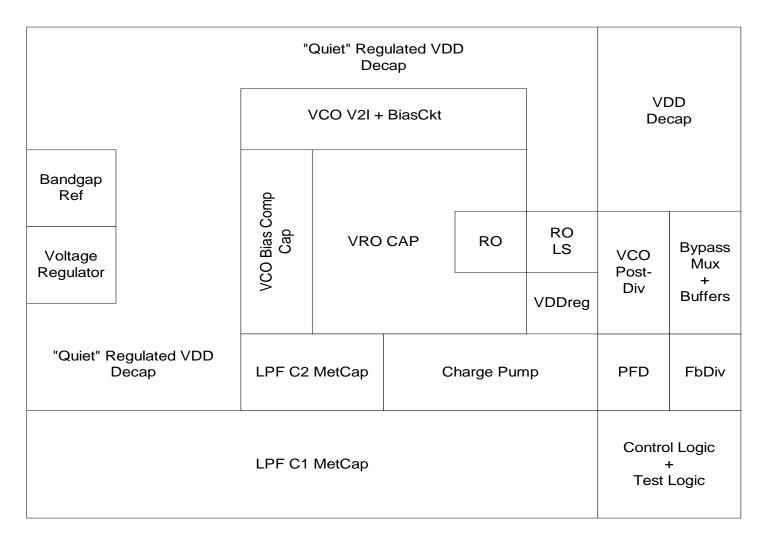

#### PLL Floorplan

#### Noise Isolation

- Check extracted netlist for coupling of switching signals onto sensitive analog signals (e.g. REFCLK  $\rightarrow$  V<sub>ctl</sub>)

- Check that LPF metal caps are present and well-connected to correct power supplies

- Check that VSS of LPF metal caps and VSS of VCO bias circuits are well-connected and at same potential

- Check that correct shields for sensitive signals are in place and well-tied to correct power supplies

#### Noise Isolation

- Account for parasitic capacitance to substrate in "NWELL" decaps, diodes, and well/diffusion resistors

- Add guard rings as applicable

- Buffer control signals and programmable inputs locally before use

- avoids problem where VSS of control signal doesn't match local VSS where signal is used

- filters coupling/glitches on long routes

# Signal EM / ESD

- Inspect wires that conduct DC current and wires that drive large switching output loads for EM violations (e.g. chargepump bias, output clocks)

- Check that signal ESD and/or power supply clamps are well-connected to power supplies (< 1-2  $\Omega$ )

- extract power grids and ESD

- simulate for voltage peaks and diodes wired-backward

#### Power-Grid IR

- Aim for avg IR drops < 5mV over entire PLL, less within and between related analog blocks

- Decoupling capacitors surround large, switching buffers to reduce IR drops and are well-connected to grid

- Check for isolated power domain islands

- Plan power domains and level-shifter placement up-front

# Switching Signals

Match differential signals – total capacitance and coupling (e.g. up, up\_x, dn, dn\_x, clk, clk\_x)

- try to match total capacitance < 1-2%

- Maintain fanout (incl. Wires) < ~6 on high-speed paths, < ~10 on DC paths (e.g. encode/decoders)</li>

- reduces crow-bar current and noise glitches

- Setup/Hold checks in PFD, Feedback Divider, and Post-VCO divider. Needs lots of margin for FBDIV to account for overshoot, aging, etc.

- strive for FBDIV faster than VCO(max)

### PLL Instantiation – Checks

- Mismatch on differential signals

- Coupling into refclk, output clocks

- Possible glitches on control inputs

- Signal routes over sensitive areas of PLL (VCO, loop filter, charge-pump)

- Large buffers on edge of PLL that may inject noise in substrate (keep-out requirement?)

#### PLL Instantiation – Checks

- Output wires wide enough to handle current load (EM)

- Rise/fall times on inputs/outputs add maxcap limit into timing file to flag heavy loads - RC delays

- VDDA/test signal routes to bumps and/or ESD

- VDD/ VSS power supply connections

## **Functional Modes**

- Power-Down/Reset/Test Modes

- chicken-and-egg start-up problems esp. level-shifters, bootstrapped regulators

- Contention?

- measure current in every device in these modes

- SLOW clock mode

- drive slow output clock at power-on to remove contentious states in downstream logic

- disable any clock gaters

- mux in separate ring oscillator or force VCO/post-VCO div to produce low frequency clock in open-loop mode

- avoid glitches when entering/leaving SLOW mode

- Frequency Hopping

- Ensure that FBDIV can't fail during frequency transition if RESET not applied

# **Power/Clocking Domains**

- Level-shifters are present when crossing power domains and are connected to correct supplies

- apply writability analysis with mismatch

- check for overstress

- easy to miss

- Add synchronizers or "walk clocks" when crossing clock domains – easy to miss

- Check metastability on flops, comparators is there a failure mechanism? Calculate MTBF.

- Insert bypass mode mux, preferably such that if the regulator fails, bypass clock still propagates to output

# RTL vs. Circuit

- Add assertions to RTL model to flag illegal input states

- Verify that RTL and tester don't assume that dividers, etc. are initialized to known states upon power-on, frequencychanges, etc. – add logic to establish determinism if needed

- Model/verify all digital logic in RTL

- Specify expected input states at boundaries of all analog blocks in various operating modes

- Take special care with calibration algorithms outside PLL

- Simulate PLL exhaustively in VerilogA, Nanosim, etc, if possible

# RTL vs. Circuit

- Look for incorrect polarity on input control signals (e.g., reset, powerDown) and REFCLK

- Look for glitches on feedback clock and other dividers

- Exercise all divider/counter states

- Check for possible VCO run-away conditions during poweron and frequency changes (e.g., no reset or feedback divider is halted)

- Verify that unselected inputs of muxes in critical signal paths are gated (e.g., VCO post-divider muxes)

## **Behavioral Simulations**

- Behavioral simulation –before detailed circuit design define requirements for each block – e.g. PLLUS, Simulink

- Develop/verify jitter budget e.g. PCI-Express

- Estimate VCO frequency overshoot

- Loop bandwidth vs. reference noise suppression

- Simulate effects of VCO gain variation, loop filter leakage, charge-pump mismatch, feedback delays, OSR, spreadspectrum tracking, Vctl-sensitive loop parameters, PFD deadzone, parasitic poles

# **Circuit Simulations**

- Start-up circuit safety margin bandgap, VCO, regulators

- Stability of all internal feedback loops

- AC and transient impulse response (ringing)

- e.g., bandgap, regulator, charge-pump bias, VCO bias

- Phase margin, gain margin, # of rings

- VCO RO stage delays rise vs. fall, stage-to-stage lower ISF

- Level-shifters' possible corruption of duty-cycle

- Switching-induced noise spikes on regulated power supplies

- Current dissipation in power

## **Circuit Simulations**

- PSRR of voltage regulators, ability of regulators to meet fast-changing current load

- Step reference phase, observe PLL re-lock

- overshoot, relock time

- Simulate entire sequence from power-on to lock

- sanity check

## **Devices/Circuits**

- Estimate effects of Vt mismatch BEFORE starting layout (monte carlo, dVt ~ 1/sqrt(W\*L))

- most sensitive: bandgap, charge-pump, other low I ckts

- Estimate loop parameter variations, static error, reference spurs due to PVT and mismatch before starting layout

- Kvco, Icp, R, C1 (also vs. Vctl) esp. dual- charge-pump designs

- circuit techniques to minimize effects: self-bias, Icp\*Rlpf=const

- self-bias not as effective if not all devices the same Leff

- Diode current density (bandgap) ideality factor may be sensitive to current density – stay away from cliff

# **Device Reliability**

- Gate Overstress

- especially likely during power-down, reset, test

- hspice .biaschk is useful

- Gate Leakage

- LPF especially,  $I_{leak}(LPF) < a$  few nA

- Switches used for test modes

- Gate loads of high-impedance nodes (e.g. bandgap)

- Large op-amp inputs

# **Device Reliability**

- Check PMOS devices for NBTI-sensitivity and NMOS devices for PBTI-sensitivity

- V<sub>gs</sub> of matched devices should be the same at all times, even when not selected (e.g. current-steering DAC) – don't place switches closest to supply rails

- switching circuits such as VCO and FBDIV should have enough frequency headroom to allow for aging. High V<sub>gs</sub> is bad! 10-20% margin?

- effects worse at sub-90nm and may not be wellmodeled

# Lithography/Devices

- Add dummy poly to reduce ACLV (across chip linewidth variation), esp. in  $L_{min}$  devices

- Maintain gate poly on fixed pitch in same orientation to reduce ACLV (esp. in  $L_{min}$  devices)

- Try to maintain constant poly density e.g. no large caps next to sensitive  $L_{min}$  devices)

- Add dummy devices if stress/strain is applied and matching is required (e.g., charge-pump)

# Tips for Design for Test

- Measuring Jitter and Phase Error

- Measuring Loop Dynamics

- Analog Measurements

- Probing

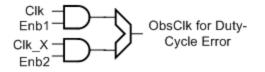

# Getting Clocks from PLL to Board

- Differential I/O outputs highly desirable to reject commonmode noise – use fastest, lowest-latency I/O available

- Divide VCO to reduce board attenuation only if necessary

→ make divider programmable

- Measuring duty-cycle

- add mux to select either true or inverted VCO clock

- Duty-cycle error = (Duty+ Duty-) / 2

- E.g. Duty(true) = 56%, Duty(inv) = 54%  $\rightarrow$ Error=1%

Copyright, Dennis Fischette, 2009

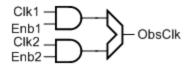

# Getting Clocks from PLL to Board

- Ability to disable neighboring I/O when measuring jitter

- Observe REF, VCO, and FBCLK. Gate all but the observed clock at the inputs of the clock observation mux to minimize coupling between clocks

Phase error measurement: trigger scope on REFCLK on board. Capture internal REFCLK and FBCLK in infinite persistence. Measure difference between internal REFCLK and FBCLK on *same* pin.

# Measuring Loop Dynamics

- Modulate reference phase at various modulation frequencies and measure VCO phase using TIE

- used to construct closed-loop transfer function

- On-chip state-machines

- range from simple to sophisticated

- disturb locked PLL in some way and observe re-lock behavior

- Need ability to measure key internal analog signals without injecting noise

- Loop filter control voltage

- Ring Oscillator regulated supply

- Bandgap reference

- Regulated power supplies

- Charge-pump bias voltages and currents

- Metrics

- Measurement BW ~ PLL Bandwidth or less

- Accuracy ~ 5mV?

- Programmable via JTAG

- Internal A/D

- Can be fairly slow

- Minimize mux switch leakage into A/D front-end

- Minimize coupling to sensitive signals

- May require external analog pin for calibration

- Compare analog voltage to internally-generated voltage reference

- Use state-machine to minimize # of comparators to save area

- Disable when not in use to save power

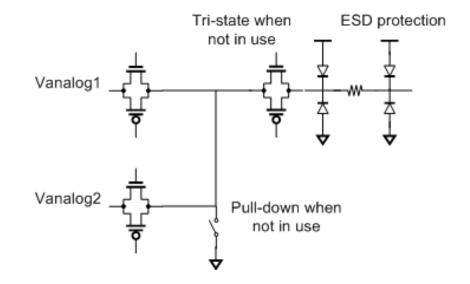

- Analog Observation Pins

- Force or sense voltage/current

- Low BW high impedance analog signals and high parasitics

- Need ESD (HBM,CDM) to protect signals –watch for leakage

- Can wire-OR analog observation pins from several PLL's but watch for increased pin leakage causing IR drops across pass-gates (e.g., 3-6kΩ) or causing high-impedance analog signals to droop

- Buffer control voltage before sending off-chip to prevent leakage and extra load from upsetting feedback loop – watch for gate leakage in unity-gain buffer

- Two-level transmission-gate analog mux connects analog signals to outside world

- Pull-down to VSS middle node of two-level mux when not in use to minimize coupling of noisy pin to analog signals (at expense of increased leakage).

# Probing On-chip (last resort!)

- If not flip-chip, then put probe pads on top-layer metal

- Probe pad size >1 $\mu$ m × 1 $\mu$ m. Prefer > 2 $\mu$ m × 2 $\mu$ m

- Place probe pad on a side-branch of analog net to avoid breaking wire with probe

- Separate probe pads to allow room for multiple probes

- FIB: can add probe pad, add or remove wires

- need room and luck

# Summary: Uncle D's PLL Top 5 List

- 1. Maintain damping factor  $\sim 1$  for low period jitter apps

- VDD-induced and intrinsic VCO noise loop can't do the work for you

- 3. Leaky loop filter gate caps will cost you your job

- 4. Make FBDIV run faster than VCO

- Observe VCO, FBCLK, REF, clkTree on differential I/O pins you can't fix what you can't see!

#### Special thanks to Alvin Loke for allowing to me "borrow" some of his diagrams and ideas for this talk...which ones? The good ones

## References

Copyright, Dennis Fischette, 2009

#### Paper References

- [1] B. Razavi, *Monolithic Phase-Locked Loops and Clock-Recovery Circuits*, IEEE Press, 1996. collection of IEEE PLL papers.

- [2] I. Young *et al.*, "A PLL clock generator with 5 to 110 MHz of lock range for microprocessors," *IEEE J. Solid-State Circuits*, vol. 27, no. 11, pp. 1599-1607, Nov. 1992.

- [3] J. Maneatis, "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques," IEEE J. Solid-State Circuits, vol. 31, no. 11, pp. 1723-1732. Nov. 1996.

- [4] J. Maneatis, "Self-Biased, High-Bandwidth, Low-Jitter 1-to-4096 Multiplier Clock Generator PLL," IEEE J. Solid-State Circuits, vol. 38, no.11, pp. 1795-1803. Nov. 2003.

- [5] F. Gardner, "Charge-pump phase-lock loops," *IEEE Trans. Comm.*, vol. COM-28, no. 11, pp 1849-1858, Nov. 1980.

- [6] V. von Kaenel, "A 32- MHz, 1.5mW @ 1.35 V CMOS PLL for Microprocessor Clock Generation," IEEE J. Solid-State Circuits, vol. 31, no. 11, pp. 1715-1722. Nov. 1996.

- [7] I. Young, "A 0.35um CMOS 3-880MHz PLL N/2 Clock Multiplier and Distribution Network with Low Jitter for Microprocessors," *Proc. ISSCC 1997*, pp. 330-331.

- [8] J. Ingino *et al.*, "A 4-GHz Clock System for a High-Performance System-on-a-Chip Design," *IEEE J. Solid-State Circuits*, vol. 36, no. 11, pp. 1693-1698. Nov. 2001.

- [9] A. Maxim *et al.*, "A Low-Jitter 125-1250 MHz Process-Independent CMOS PLL Based on a Sample-Reset Loop Filter," *Proc. ISSCC 2001*, pp. 394-395.

- [10] N.Kurd *et al.*, "A Replica-Biased 50% Duty Cycle PLL Architecture with 1X VCO," *Proc. ISSCC 2003*, pp.426-427.

- [11] K. Wong, *et al.*, "Cascaded PLL Design for a 90nm CMOS High Performance Microprocessor," *Proc. ISSCC 2003*, pp.422-423.

#### Paper References

- [12] M. Mansuri, et al., "A Low-Power Adaptive-Bandwidth PLL and Clock Buffer With Supply-Noise Compensation", IEEE J. Solid-State Circuits, vol. 38, no.11, pp. 1804-1812. Nov. 2003.

- [13] A. Maxim, "A 160-2550 MHz CMOS Active Clock Deskewing PLL Using Analog Phase Interpolation," *Proc. ISSCC 2004*, pp. 346-347.

- [14] J. Lin *et al*, "A PVT Tolerant 0.18MHz to 660MHz Self-Calibrated Digital PLL in 90nm CMOS Process," *Proc. ISSCC 2004*, pp. 488-489.

- [15] J. McNeill, "Jitter in Ring Oscillators," *IEEE J. Solid-State Circuits*, vol. 32, no.6, pp. 870-878, Jun. 1997.

- [16] A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no.8, pp. 1803-1816, Aug. 2006.

- [17] L. Dai et al., "Design of Low-Phase-Noise CMOS Ring Oscillators," IEEE Trans. Circuits and Systems-II: Analog and Digital Signal Processing, vol. 49, no. 5, pp. 328-338, May 2002.

- [18] U. Moon et al., "Spectral Analysis of Time-Domain Phase Jitter Measurements," IEEE Trans. Circuits and Systems-II: Analog and Digital Signal Processing, vol. 49, no. 5, pp. 321-327, May 2002

- [19] J. Kim et al., "Design of CMOS Adaptive-Bandwidth PLL/DLLs: A General Approach," IEEE Trans. Circuits and Systems-II: Analog and Digital Signal Processing, vol. 50, no. 11, pp. 860-869, Nov 2003.

- [20] T. Toifl et al., "A 0.94-ps-RMS-Jitter 0.016-mm<sup>2</sup> 2.5-GHz Multiphase Generator PLL with 360 Degree Digitally Programmable Phase Shift for 100Gb/s Serial Links," IEEE J. Solid-State Circuits, vol. 40, no.12, pp. 2700-2711, Dec. 2005.

- [21] S. Wedge, "Predicting Random Jitter," *IEEE Circuits & Devices Magazine*, pp. 31-38, Nov/Dec 2006.

- [22] A. Rylyakov et al., "A Wide Power-Supply Range (0.5V-to1.3V) Wide Tuning Range (500MHz-to-8GHz) All Static CMOS AD PLL in 65nm CMOS SOI," Proc. ISSCC 2007, pp. 172-173.

Copyright, Dennis Fischette, 2009

#### **Paper References**

- [24] R. Staszewski *et al*, "All-Digital PLL and Transmitter for Mobile Phones," *IEEE J. Solid-State Circuits*, vol. 40, no.12, pp. 2469-2482. Dec. 2005.

- [25] R. Staszewski *et al*, "All-Digital PLL with Ultra Fast Settling," *IEEE Trans. On Circuits and Systems II: Express Briefs*, vol. 54, no.2, pp. 181-185. Feb. 2007.

- [26] V. Kratyuk *et al*, "A Design Procedure for All-Digital Phase-Locked Loops Based on a Charge-Pump Phase-Locked-Loop Analogy," *IEEE Trans. On Circuits and Systems II: Express Briefs*, vol. 54, no.3, pp. 247-251. Mar. 2007.

- [27] J. Hein *et al*, "z-Domain Model for Discrete-Time PLL's," *IEEE Trans. On Circuits and Systems*, vol. 35, no.11, pp. 1393-1400. Nov. 1988.

#### Monograph References

- [1] B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw-Hill, 2001.

- [2] R. Best, *Phase-Locked Loops, McGraw*-Hill, 1993.

- [3] R. Dorf, Modern Control Theory, 4th Edition, Addison-Wesley, 1986.

- [4] P.Gray and R. Meyer, Analysis and Design of Analog Integrated Circuits, 3<sup>rd</sup> Edition, J.

Wiley & Sons, 1993.

- [5] K. Bernstein and N. Rohner, *SOI Circuit Design Concepts*, Kluwer Academic Publishers, 2000.

- [6] A. Hajimiri and T. Lee, *The Design of Low Noise Oscillators*, Kluwer Academic Publishers, 1999.

- [7] T. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, Cambridge University Press, 1998.

- [8] F. Gardner, *Phaselock Techniques*, 3rd Edition, New York, Wiley & Sons, 2005.

Copyright, Dennis Fischette, 2009

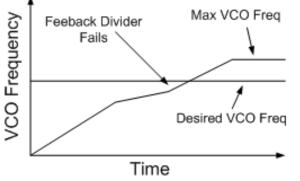

- Observation is that VCO frequency is pinned at max value. Can't observe Vctl or feedback clock. VCO fails to oscillate at low frequency because of insufficient gain in 3-stage VCO. When VCO finally starts, FBDIV can't keep up, causing "runaway" Solution: increase gain of delay stage and FBDIV speed.

- VCO "run-away" when re-locking to higher frequency due to VCO overshoot and slow FBDIV.

- VCO loses lock occasionally at low frequencies. Due to insufficient VCO level-shifter gain. Dropped VCO edges. Required real-time scope for debug

- High jitter at low VCO frequencies due to Vctl approaching Vt of V2I current source. Solution: operate VCO at 2X.

- Occasional high deterministic jitter caused by coupling into PLL's VDDA bondwire.

- Extremely high period jitter caused by incorrect wiring of 8-bit charge-pump setting. Bandwidth much too high. Verilog model did not check for legal input settings.

- PLL won't start-up at low temp due to weak start-up circuit in voltage regulator and lack of simulation at corners with slow VDDA ramp-rate.

- PLL period modulated strongly by 400MHz signal, resulting from oscillating internal feedback loop in VCO bias ckts. Ultimate cause, fab misprocessing of compensation cap and insufficient margin in ckt.

- Metastability condition corrupted digital loop filter due to slow devices, low Vdd, and insufficient design margin.

- Digital VCO out-of-range due to resistor mis-processing. Solution: fusable chicken-bits to adjust frequency range.

- Race condition in digital loop filter caused by missing synchronizers in clock domain crossing.

- CDM ESD failures of analog measurement pins no visual inspection and no extraction/simulation of connection to VSS.

- Duty-cycle corruption (> 57%) caused by unbalanced fanouts in delay stages after VCO – exacerbated by singleended clocking.

- Contention in analog observation signals due to ESD diodes wired backward and control logic bugs.

- Inconsistent duty cycle. Failure to initialize state in post-VCO divider exposed VCO duty-cycle error.